2024. 11. 19. 15:57ㆍ디바이스 드라이버

Makefile 이란?

Makefile이란 일종의 빌드시스템이다. 리눅스 개발 환경 이해하기 마지막 부분에서 gcc명령어 하나로 링크까지 할 수 있지만, 사실 대부분은 링크와 컴파일을 분리해서 사용한다. 그 이유는 점진적으로 빌드하기 위해서이다. 간단한 프로그램이야 한꺼번에 컴파일해도 시간이 오래걸리지 않겠지만, 프로그램이 사용하는 파일들이 많아지고, 그 파일들이 복잡하게 얽혀있다면 모든 파일들을 컴파일하는데는 시간이 오래걸릴 것이다.

그래서 개발자들은 빌드시스템을 사용해서 수정한 부분과 그에 대해 의존성이 있는 부분만 컴파일하여 시간을 단축시킨다.

Makefile의 구성

타겟 (Target) : 생성하고자 하는 것

의존성 (Dependency) : 필요한 것

명령어 (Command) : 해야하는 것

으로 구성되어 있다.

Makefile의 구성 예시이다.

PHONY를 생성하기 위해서는 Target2가 필요하다.

Target2를 생성하기 위해서는 Dependency3와 Target1이 필요하고, 만약 의존성이 충족되면 Command3를 실행한다.

Target1을 생성하기 위해서는 Dependency1과 Dependency2가 필요하고, 의존성이 충족되면 Command1과 Command2를 실행한다.

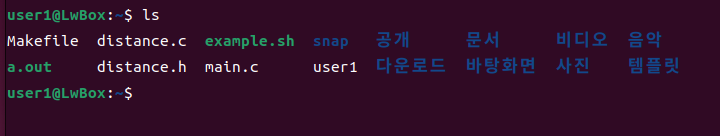

저번에 리눅스 개발 환경 이해하기 부분에서 사용했던 예제를 Makefile로 만들었다.

기존에 있던 example,main.o,distance.o 파일을 지우고 make를 하면

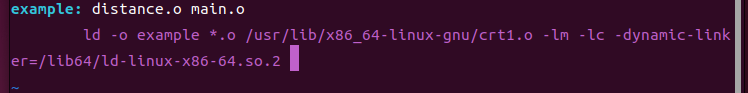

make파일 안에 있던 명령들이 실행된다.

먼저 example파일을 만들기 위해서는 distance.o와 main.o가 필요하다 main.o 부분에서 main.c가 존재하기 때문에 밑에 있는 Command를 실행한다.

마찬가지로 distance.o 부분에서도 distance.c가 존재하기 때문에 밑에 있는 Command를 실행한다. 마지막으로 distance.o와 main.o가 존재하기 때문에 example 밑에 있는 Command를 실행하고 example파일이 생성된다.

main.c를 간단하게 수정만 해보겠다. return -> Return으로 수정하고 make를 하면

다음과 같이 실행된다. 위에 있던 처음 make 결과와의 차이점은 main과 관련없는 distance의 Command는 실행이 되지 않았다는 점이다. 이로인해 빌드시스템을 사용하면 점진적인 빌드를 사용할 수 있다는 점을 알 수 있다.

한 가지 팁이 있다면,

이런식으로 gcc 명령어 부분을 생략해도 기본으로 실행시켜주기 때문에 example파일이 make가 된다.

gcc 명령어가 있을 때와 동일하게 gcc 명령어가 실행되는 모습을 볼 수 있다.

'디바이스 드라이버' 카테고리의 다른 글

| 리눅스 커널 빌드하기 (1) | 2024.11.21 |

|---|---|

| Rootfs 빌드 하기 (0) | 2024.11.20 |

| 리눅스 개발 환경 이해하기 (2) (0) | 2024.11.19 |

| 리눅스 개발 환경 이해하기 (1) (1) | 2024.11.15 |

| Shell script (빈 디렉토리에 .gitkeep파일 생성하기 (0) | 2024.11.14 |